# **Trusted Firmware-A**

unknown

## **CONTENTS**

| 1   | About                      | 1   |

|-----|----------------------------|-----|

| 2   | Getting Started            | 27  |

| 3   | Processes & Policies       | 111 |

| 4   | Components                 | 141 |

| 5   | System Design              | 263 |

| 6   | Platform Ports             | 363 |

| 7   | Performance & Testing      | 471 |

| 8   | Security Advisories        | 479 |

| 9   | Design Documents           | 491 |

| 10  | Threat Model               | 505 |

| 11  | Change Log & Release Notes | 531 |

| 12  | Glossary                   | 623 |

| 13  | License                    | 627 |

| 14  | Getting Started            | 629 |

| Inc | dex                        | 631 |

**CHAPTER**

ONE

#### **ABOUT**

#### 1.1 Feature Overview

This page provides an overview of the current *TF-A* feature set. For a full description of these features and their implementation details, please see the documents that are part of the *Components* and *System Design* chapters.

The Change Log & Release Notes provides details of changes made since the last release.

#### 1.1.1 Current features

- Initialization of the secure world, for example exception vectors, control registers and interrupts for the platform.

- Library support for CPU specific reset and power down sequences. This includes support for errata workarounds and the latest Arm DynamIQ CPUs.

- Drivers to enable standard initialization of Arm System IP, for example Generic Interrupt Controller (GIC), Cache Coherent Interconnect (CCI), Cache Coherent Network (CCN), Network Interconnect (NIC) and Trust-Zone Controller (TZC).

- A generic *SCMI* driver to interface with conforming power controllers, for example the Arm System Control Processor (SCP).

- SMC (Secure Monitor Call) handling, conforming to the SMC Calling Convention using an EL3 runtime services framework.

- *PSCI* library support for CPU, cluster and system power management use-cases. This library is pre-integrated with the AArch64 EL3 Runtime Software, and is also suitable for integration with other AArch32 EL3 Runtime Software, for example an AArch32 Secure OS.

- A minimal AArch32 Secure Payload (SP\_MIN) to demonstrate PSCI library integration with AArch32 EL3 Runtime Software.

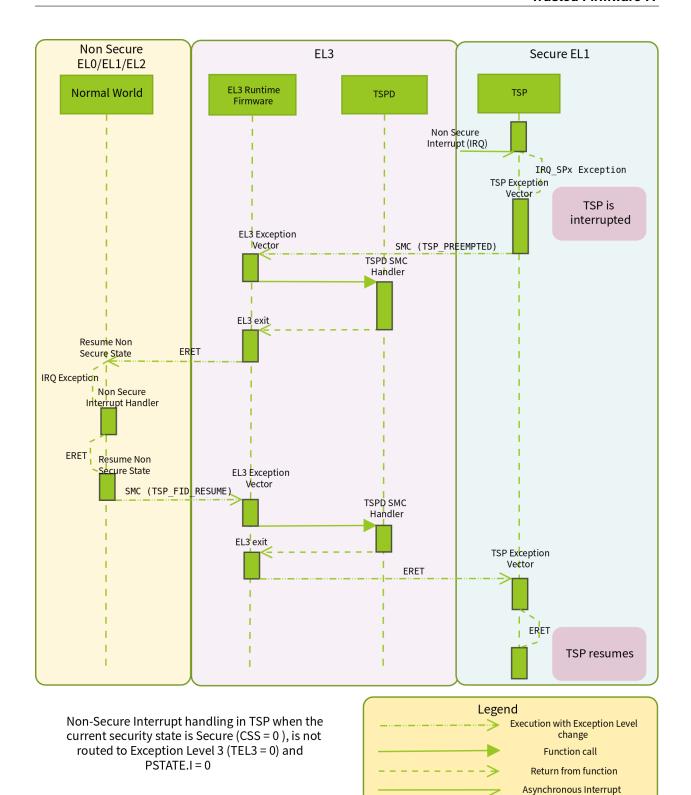

- Secure Monitor library code such as world switching, EL1 context management and interrupt routing. When a Secure-EL1 Payload (SP) is present, for example a Secure OS, the AArch64 EL3 Runtime Software must be integrated with a Secure Payload Dispatcher (SPD) component to customize the interaction with the SP.

- A Test SP and SPD to demonstrate AArch64 Secure Monitor functionality and SP interaction with PSCI.

- SPDs for the OP-TEE Secure OS, NVIDIA Trusted Little Kernel and Trusty Secure OS.

- A Trusted Board Boot implementation, conforming to all mandatory TBBR requirements. This includes image authentication, Firmware Update (or recovery mode), and packaging of the various firmware images into a Firmware Image Package (FIP).

- Pre-integration of TBB with the Arm CryptoCell product, to take advantage of its hardware Root of Trust and crypto acceleration services.

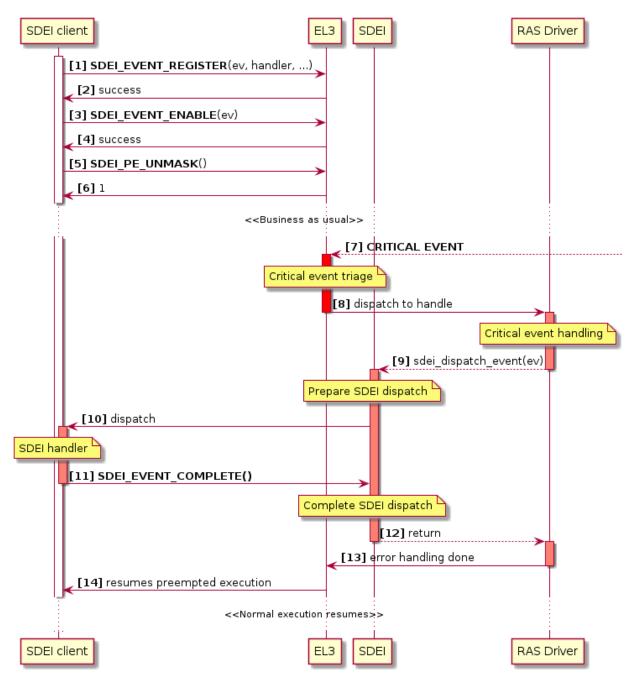

- Reliability, Availability, and Serviceability (RAS) functionality, including

- A Secure Partition Manager (SPM) to manage Secure Partitions in Secure-EL0, which can be used to implement simple management and security services.

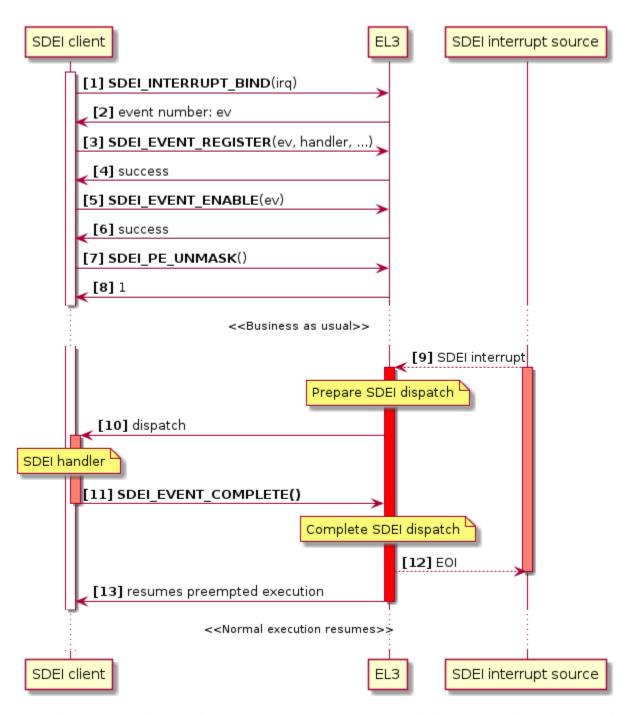

- An SDEI dispatcher to route interrupt-based SDEI events.

- An Exception Handling Framework (EHF) that allows dispatching of EL3 interrupts to their registered handlers, to facilitate firmware-first error handling.

- A dynamic configuration framework that enables each of the firmware images to be configured at runtime if required by the platform. It also enables loading of a hardware configuration (for example, a kernel device tree) as part of the FIP, to be passed through the firmware stages. This feature is now incorporated inside the firmware configuration framework (fconf).

- Support for alternative boot flows, for example to support platforms where the EL3 Runtime Software is loaded

using other firmware or a separate secure system processor, or where a non-TF-A ROM expects BL2 to be loaded

at EL3.

- Support for the GCC, LLVM and Arm Compiler 6 toolchains.

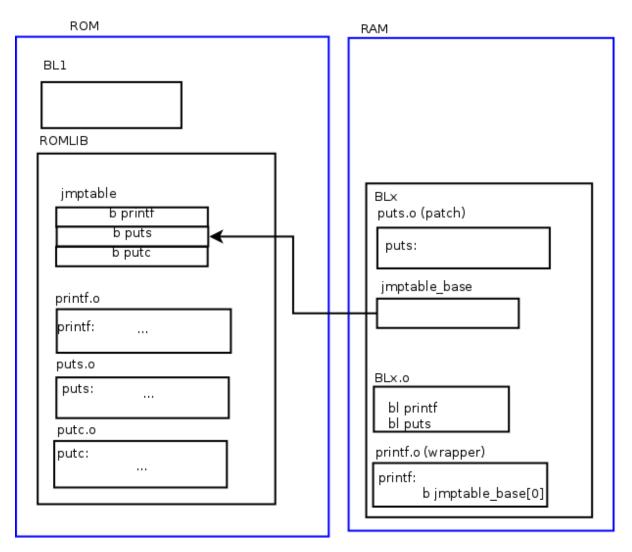

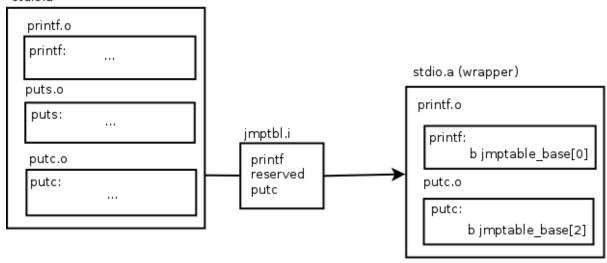

- Support for combining several libraries into a "romlib" image that may be shared across images to reduce memory

footprint. The romlib image is stored in ROM but is accessed through a jump-table that may be stored in readwrite memory, allowing for the library code to be patched.

- Support for the Secure Partition Manager Dispatcher (SPMD) component as a new standard service.

- Support for ARMv8.3 pointer authentication in the normal and secure worlds. The use of pointer authentication

in the normal world is enabled whenever architectural support is available, without the need for additional build

flags.

- Position-Independent Executable (PIE) support. Currently for BL2, BL31, and TSP, with further support to be added in a future release.

#### 1.1.2 Still to come

- Support for additional platforms.

- Refinements to Position Independent Executable (PIE) support.

- Continued support for the FF-A v1.0 (formally known as SPCI) specification, to enable the use of secure partition

management in the secure world.

- Documentation enhancements.

- Ongoing support for new architectural features, CPUs and System IP.

- Ongoing support for new Arm system architecture specifications.

- Ongoing security hardening, optimization and quality improvements.

Copyright (c) 2019-2021, Arm Limited. All rights reserved.

## 1.2 Release Processes

## 1.2.1 Project Release Cadence

The project currently aims to do a release once every 6 months which will be tagged on the master branch. There will be a code freeze (stop merging non-essential changes) up to 4 weeks prior to the target release date. The release candidates will start appearing after this and only bug fixes or updates required for the release will be merged. The maintainers are free to use their judgement on what changes are essential for the release. A release branch may be created after code freeze if there are significant changes that need merging onto the integration branch during the merge window.

The release testing will be performed on release candidates and depending on issues found, additional release candidates may be created to fix the issues.

```

|<-----6 months----->|

|<---4 weeks--->| |<---4 weeks--->|

+-----> time

| code freeze ver w.x code freeze ver y.z

```

#### **Upcoming Releases**

These are the estimated dates for the upcoming release. These may change depending on project requirement and partner feedback.

| Release Version | Target Date         | Expected Code Freeze |  |

|-----------------|---------------------|----------------------|--|

| v2.0            | 1st week of Oct '18 | 1st week of Sep '18  |  |

| v2.1            | 5th week of Mar '19 | 1st week of Mar '19  |  |

| v2.2            | 4th week of Oct '19 | 1st week of Oct '19  |  |

| v2.3            | 4th week of Apr '20 | 1st week of Apr '20  |  |

| v2.4            | 2nd week of Nov '20 | 4th week of Oct '20  |  |

| v2.5            | 3rd week of May '21 | 5th week of Apr '21  |  |

| v2.6            | 4th week of Nov '21 | 2nd week of Nov '21  |  |

## 1.2.2 Removal of Deprecated Interfaces

As mentioned in the *Platform Compatibility Policy*, this is a live document cataloging all the deprecated interfaces in TF-A project and the Release version after which it will be removed.

| Interface | Deprecation Date | Removed after Release | Comments |

|-----------|------------------|-----------------------|----------|

|           |                  |                       |          |

Copyright (c) 2018-2021, Arm Limited and Contributors. All rights reserved.

1.2. Release Processes 3

## 1.3 Project Maintenance

Trusted Firmware-A (TF-A) is an open governance community project. All contributions are ultimately merged by the maintainers listed below. Technical ownership of most parts of the codebase falls on the code owners listed below. An acknowledgement from these code owners is required before the maintainers merge a contribution.

More details may be found in the Project Maintenance Process document.

#### 1.3.1 Maintainers

Mail Dan Handley <an.handley@arm.com>

GitHub ID danh-arm

Mail Soby Mathew <soby.mathew@arm.com>

GitHub ID soby-mathew

Mail Sandrine Bailleux <sandrine.bailleux@arm.com>

GitHub ID sandrine-bailleux-arm

Mail Alexei Fedorov < Alexei.Fedorov@arm.com>

GitHub ID AlexeiFedorov

Mail Manish Pandey <manish.pandey2@arm.com>

GitHub ID manish-pandey-arm

Mail Mark Dykes <mark.dykes@arm.com>

GitHub ID mardyk01

Mail Olivier Deprez <olivier.deprez@arm.com>

GitHub ID odeprez

Mail Bipin Ravi <br/> <br/> bipin.ravi@arm.com>

GitHub ID bipinravi-arm

Mail Joanna Farley <joanna.farley@arm.com>

GitHub ID joannafarley-arm

Mail Julius Werner < jwerner@chromium.org>

GitHub ID jwerner-chromium

Mail Varun Wadekar < vwadekar@nvidia.com>

GitHub ID vwadekar

Mail Andre Przywara <andre.przywara@arm.com>

GitHub ID Andre-ARM

Mail Lauren Wehrmeister < Lauren. Wehrmeister @ arm.com>

GitHub ID laurenw-arm

Mail Madhukar Pappireddy < Madhukar. Pappireddy @arm.com>

GitHub ID madhukar-Arm

Mail Raghu Krishnamurthy <raghu.ncstate@icloud.com>

#### GitHub ID raghuncstate

#### 1.3.2 Code owners

#### **Common Code**

#### Armv7-A architecture port

Mail Etienne Carriere <etienne.carriere@linaro.org>

GitHub ID etienne-lms

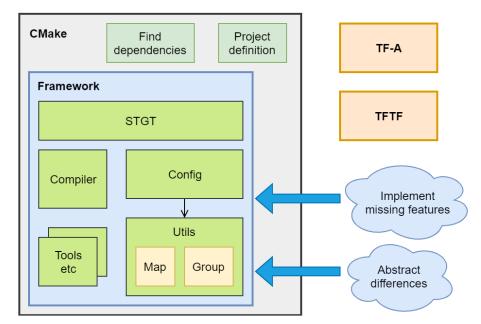

#### **Build Definitions for CMake Build System**

```

Mail Javier Almansa Sobrino <Javier.AlmansaSobrino@arm.com>

GitHub ID javieralso-arm

Mail Chris Kay <chris.kay@arm.com>

GitHub ID CJKay

Files /

```

#### **Software Delegated Exception Interface (SDEI)**

```

Mail Mark Dykes <mark.dykes@arm.com>

GitHub ID mardyk01

Mail John Powell <john.powell@arm.com>

GitHub ID john-powell-arm

Files services/std_svc/sdei/

```

#### **Trusted Boot**

```

Mail Sandrine Bailleux <sandrine.bailleux@arm.com>

GitHub ID sandrine-bailleux-arm

Mail Manish Pandey <manish.pandey2@arm.com>

GitHub ID manish-pandey-arm

Mail Manish Badarkhe <manish.badarkhe@arm.com>

GitHub ID ManishVB-Arm

Files drivers/auth/

```

#### **Secure Partition Manager (SPM)**

Mail Olivier Deprez <olivier.deprez@arm.com>

GitHub ID odeprez

Mail Manish Pandey <manish.pandey2@arm.com>

GitHub ID manish-pandey-arm

Mail Maksims Svecovs <maksims.svecovs@arm.com>

GitHub ID max-shvetsov

Mail Joao Alves < Joao. Alves @ arm.com>

GitHub ID J-Alves

Files services/std\_svc/spm\*

#### **Exception Handling Framework (EHF)**

Mail Manish Badarkhe <manish.badarkhe@arm.com>

GitHub ID ManishVB-Arm

Mail John Powell < john.powell@arm.com>

GitHub ID john-powell-arm

Files bl31/ehf.c

#### **Realm Management Extension (RME)**

Mail Bipin Ravi <br/> <br/> bipin.ravi@arm.com>

GitHub ID bipinravi-arm

Mail Mark Dykes <mark.dykes@arm.com>

GitHub ID mardyk01

Mail John Powell < john.powell@arm.com>

GitHub ID john-powell-arm

Mail Zelalem Aweke <Zelalem.Aweke@arm.com>

GitHub ID zelalem-aweke

#### **Drivers, Libraries and Framework Code**

#### **Console API framework**

Mail Julius Werner < jwerner@chromium.org>

GitHub ID jwerner-chromium

Files drivers/console/

Files include/drivers/console.h

Files plat/common/aarch64/crash\_console\_helpers.S

#### coreboot support libraries

Mail Julius Werner < jwerner@chromium.org>

GitHub ID jwerner-chromium

Files drivers/coreboot/

Files include/drivers/coreboot/

Files include/lib/coreboot.h

Files lib/coreboot/

#### eMMC/UFS drivers

Mail Haojian Zhuang <a href="mailto:kaojian.zhuang@linaro.org">haojian.zhuang@linaro.org</a>

GitHub ID hzhuang1

Files drivers/partition/

Files drivers/synopsys/emmc/

Files drivers/synopsys/ufs/

Files drivers/ufs/

Files include/drivers/dw\_ufs.h

Files include/drivers/ufs.h

Files include/drivers/synopsys/dw\_mmc.h

#### JTAG DCC console driver

M Michal Simek <michal.simek@xilinx.com>

G michalsimek

M Venkatesh Yadav Abbarapu < venkatesh.abbarapu@xilinx.com>

G venkatesh

F drivers/arm/dcc/

F include/drivers/arm/dcc.h

#### **Power State Coordination Interface (PSCI)**

Mail Javier Almansa Sobrino <Javier. Almansa Sobrino @arm.com>

GitHub ID javieralso-arm

Mail Madhukar Pappireddy < Madhukar. Pappireddy @arm.com>

GitHub ID madhukar-Arm

Mail Lauren Wehrmeister <Lauren.Wehrmeister@arm.com>

GitHub ID laurenw-arm

Mail Zelalem Aweke <Zelalem.Aweke@arm.com>

GitHub ID zelalem-aweke

Files lib/psci/

#### **DebugFS**

Mail Olivier Deprez <olivier.deprez@arm.com>

GitHub ID odeprez

Files lib/debugfs/

#### Firmware Configuration Framework (FCONF)

Mail Madhukar Pappireddy < Madhukar. Pappireddy @ arm.com>

GitHub ID madhukar-Arm

Mail Manish Badarkhe <manish.badarkhe@arm.com>

GitHub ID ManishVB-Arm

Mail Lauren Wehrmeister <Lauren.Wehrmeister@arm.com>

GitHub ID laurenw-arm

Files lib/fconf/

#### **Performance Measurement Framework (PMF)**

Mail Joao Alves < Joao. Alves @ arm.com>

**GitHub ID** J-Alves

Mail Jimmy Brisson < Jimmy.Brisson@arm.com>

GitHub ID theotherjimmy

Files lib/pmf/

#### **Arm CPU libraries**

Mail Lauren Wehrmeister <Lauren.Wehrmeister@arm.com>

GitHub ID laurenw-arm

Mail John Powell < john.powell@arm.com>

GitHub ID john-powell-arm

Files lib/cpus/

#### Reliability Availability Serviceabilty (RAS) framework

Mail Olivier Deprez <olivier.deprez@arm.com>

GitHub ID odeprez

Mail Manish Pandey <manish.pandey2@arm.com>

GitHub ID manish-pandey-arm

Files lib/extensions/ras/

## **Activity Monitors Unit (AMU) extensions**

Mail Alexei Fedorov < Alexei.Fedorov@arm.com>

GitHub ID AlexeiFedorov

Mail Chris Kay <chris.kay@arm.com>

GitHub ID CJKay

Files lib/extensions/amu/

#### Memory Partitioning And Monitoring (MPAM) extensions

Mail Zelalem Aweke <Zelalem.Aweke@arm.com>

GitHub ID zelalem-aweke

Mail Jimmy Brisson < Jimmy.Brisson@arm.com>

GitHub ID theotherjimmy

Files lib/extensions/mpam/

#### Pointer Authentication (PAuth) and Branch Target Identification (BTI) extensions

Mail Alexei Fedorov < Alexei.Fedorov@arm.com>

GitHub ID AlexeiFedorov

Mail Zelalem Aweke <Zelalem.Aweke@arm.com>

GitHub ID zelalem-aweke

Files lib/extensions/pauth/

#### **Statistical Profiling Extension (SPE)**

Mail Zelalem Aweke <Zelalem.Aweke@arm.com>

GitHub ID zelalem-aweke

Mail Jimmy Brisson < Jimmy.Brisson@arm.com>

GitHub ID theotherjimmy

Files lib/extensions/spe/

#### Scalable Vector Extension (SVE)

Mail Jimmy Brisson < Jimmy.Brisson@arm.com>

GitHub ID theotherjimmy

Files lib/extensions/sve/

#### Standard C library

Mail Alexei Fedorov < Alexei.Fedorov@arm.com>

GitHub ID AlexeiFedorov

Mail John Powell < john.powell@arm.com>

GitHub ID john-powell-arm

Files lib/libc/

#### **Library At ROM (ROMlib)**

Mail Madhukar Pappireddy < Madhukar. Pappireddy @arm.com>

GitHub ID madhukar-Arm

Files lib/romlib/

#### Translation tables (xlat\_tables) library

Mail Javier Almansa Sobrino < Javier. Almansa Sobrino @arm.com>

GitHub ID javieralso-arm

Mail Joao Alves < Joao. Alves @ arm.com>

GitHub ID J-Alves

Files lib/xlat\_tables\_\*/

#### **IO** abstraction layer

Mail Manish Pandey <manish.pandey2@arm.com>

GitHub ID manish-pandey-arm

Mail Olivier Deprez <olivier.deprez@arm.com>

GitHub ID odeprez

Files drivers/io/

#### **GIC** driver

Mail Alexei Fedorov < Alexei.Fedorov@arm.com>

GitHub ID AlexeiFedorov

Mail Manish Pandey <manish.pandey2@arm.com>

GitHub ID manish-pandey-arm

Mail Madhukar Pappireddy < Madhukar. Pappireddy @ arm.com>

GitHub ID madhukar-Arm

Mail Olivier Deprez <olivier.deprez@arm.com>

GitHub ID odeprez

Files drivers/arm/gic/

#### Libfdt wrappers

Mail Madhukar Pappireddy < Madhukar.Pappireddy@arm.com>

GitHub ID madhukar-Arm

Mail Manish Badarkhe <manish.badarkhe@arm.com>

GitHub ID ManishVB-Arm

Files common/fdt\_wrappers.c

#### **Firmware Encryption Framework**

Mail Sumit Garg <sumit.garg@linaro.org>

GitHub ID b49020

Files drivers/io/io\_encrypted.c

Files include/drivers/io/io\_encrypted.h

Files include/tools\_share/firmware\_encrypted.h

#### **Measured Boot**

Mail Alexei Fedorov < Alexei.Fedorov@arm.com>

GitHub ID AlexeiFedorov

Mail Javier Almansa Sobrino < Javier. Almansa Sobrino @arm.com>

GitHub ID javieralso-arm

Files drivers/measured\_boot

Files include/drivers/measured\_boot

Files plat/arm/board/fvp/fvp\_measured\_boot.c

#### System Control and Management Interface (SCMI) Server

Mail Etienne Carriere <etienne.carriere@st.com>

GitHub ID etienne-lms

Mail Peng Fan <peng.fan@nxp.com>

GitHub ID MrVan

Files drivers/scmi-msg

Files include/drivers/scmi\*

#### **Max Power Mitigation Mechanism (MPMM)**

Mail Chris Kay <chris.kay@arm.com>

GitHub ID CJKay

Files include/lib/mpmm/

Files lib/mpmm/

#### **Granule Protection Tables Library (GPT-RME)**

Mail Mark Dykes <mark.dykes@arm.com>

GitHub ID mardyk01

Mail John Powell < john.powell@arm.com>

GitHub ID john-powell-arm

Files lib/gpt\_rme

Files include/lib/gpt\_rme

#### **Platform Ports**

#### Allwinner ARMv8 platform port

Mail Andre Przywara <andre.przywara@arm.com>

GitHub ID Andre-ARM

Mail Samuel Holland <samuel@sholland.org>

GitHub ID smaeul

Files docs/plat/allwinner.rst

Files plat/allwinner/

Files drivers/allwinner/

#### Amlogic Meson S905 (GXBB) platform port

Mail Andre Przywara <andre.przywara@arm.com>

GitHub ID Andre-ARM

Files docs/plat/meson-gxbb.rst

Files drivers/amlogic/

Files plat/amlogic/gxbb/

#### Amlogic Meson S905x (GXL) platform port

Mail Remi Pommarel <repk@triplefau.lt>

GitHub ID remi-triplefault

Files docs/plat/meson-gxl.rst

Files plat/amlogic/gxl/

#### Amlogic Meson S905X2 (G12A) platform port

Mail Carlo Caione <ccaione@baylibre.com>

GitHub ID carlocaione

Files docs/plat/meson-g12a.rst

Files plat/amlogic/g12a/

#### Amlogic Meson A113D (AXG) platform port

Mail Carlo Caione <ccaione@baylibre.com>

GitHub ID carlocaione

Files docs/plat/meson-axg.rst

Files plat/amlogic/axg/

#### **Arm FPGA platform port**

Mail Andre Przywara <andre.przywara@arm.com>

GitHub ID Andre-ARM

Mail Javier Almansa Sobrino < Javier. Almansa Sobrino @arm.com>

GitHub ID javieralso-arm

Files plat/arm/board/arm\_fpga

#### **Arm FVP Platform port**

Mail Manish Pandey <manish.pandey2@arm.com>

GitHub ID manish-pandey-arm

Mail Madhukar Pappireddy < Madhukar. Pappireddy @ arm.com>

GitHub ID madhukar-Arm

Files plat/arm/board/fvp

#### **Arm Juno Platform port**

Mail Manish Pandey <manish.pandey2@arm.com>

GitHub ID manish-pandey-arm

Mail Chris Kay <chris.kay@arm.com>

GitHub ID CJKay

Files plat/arm/board/juno

#### **Arm Morello and N1SDP Platform ports**

Mail Manoj Kumar <manoj.kumar3@arm.com>

GitHub ID manojkumar-arm

Mail Chandni Cherukuri <chandni.cherukuri@arm.com>

GitHub ID chandnich

Files plat/arm/board/morello

**Files** plat/arm/board/n1sdp

#### **Arm Rich IoT Platform ports**

Mail Abdellatif El Khlifi <abdellatif.elkhlifi@arm.com>

GitHub ID abdellatif-elkhlifi

Mail Vishnu Banavath < vishnu.banavath@arm.com>

GitHub ID vishnu-banavath

Files plat/arm/board/corstone700

Files plat/arm/board/a5ds

Files plat/arm/board/diphda

#### **Arm Reference Design platform ports**

Mail Thomas Abraham <thomas.abraham@arm.com>

GitHub ID thomas-arm

Mail Vijayenthiran Subramaniam <vijayenthiran.subramaniam@arm.com>

GitHub ID vijayenthiran-arm

Files plat/arm/css/sgi/

Files plat/arm/board/rde1edge/

Files plat/arm/board/rdn1edge/

Files plat/arm/board/rdn2/

Files plat/arm/board/rdv1/

**Files** plat/arm/board/rdv1mc/

Files plat/arm/board/sgi575/

#### **Arm Total Compute platform port**

Mail Arunachalam Ganapathy <arunachalam.ganapathy@arm.com>

GitHub ID arugan02

Mail Usama Arif <usama.arif@arm.com>

GitHub ID uarif1

Files plat/arm/board/tc

#### HiSilicon HiKey and HiKey960 platform ports

Mail Haojian Zhuang <a href="mailto:kaojian.zhuang@linaro.org">haojian.zhuang@linaro.org</a>

GitHub ID hzhuang1

Files docs/plat/hikey.rst

Files docs/plat/hikey960.rst

Files plat/hisilicon/hikey/

Files plat/hisilicon/hikey960/

#### **HiSilicon Poplar platform port**

Mail Shawn Guo <shawn.guo@linaro.org>

GitHub ID shawnguo2

Files docs/plat/poplar.rst

Files plat/hisilicon/poplar/

#### Intel SocFPGA platform ports

Mail Tien Hock Loh <tien.hock.loh@intel.com>

GitHub ID thloh85-intel

Mail Hadi Asyrafi <muhammad.hadi.asyrafi.abdul.halim@intel.com>

GitHub ID mabdulha

Files plat/intel/soc

Files drivers/intel/soc/

#### MediaTek platform ports

Mail Rex-BC Chen <rex-bc.chen@mediatek.com>

GitHub ID mtk-rex-bc-chen

Files plat/mediatek/

#### Marvell platform ports and SoC drivers

Mail Konstantin Porotchkin <kostap@marvell.com>

GitHub ID kostapr

Files docs/plat/marvell/

Files plat/marvell/

Files drivers/marvell/

Files tools/marvell/

#### **NVidia platform ports**

Mail Varun Wadekar < vwadekar@nvidia.com>

GitHub ID vwadekar

Files docs/plat/nvidia-tegra.rst

Files include/lib/cpus/aarch64/denver.h

Files lib/cpus/aarch64/denver.S

Files plat/nvidia/

#### **NXP QorlQ Layerscape platform ports**

Mail Jiafei Pan <jiafei.pan@nxp.com>

GitHub ID qoriq-open-source

Files docs/plat/ls1043a.rst

Files plat/layerscape/

#### NXP i.MX 7 WaRP7 platform port and SoC drivers

Mail Bryan O'Donoghue <br/> <br/> bryan.odonoghue@linaro.org>

GitHub ID bryanodonoghue

Mail Jun Nie <jun.nie@linaro.org>

GitHub ID niej

Files docs/plat/warp7.rst

Files plat/imx/common/

Files plat/imx/imx7/

Files drivers/imx/timer/

Files drivers/imx/uart/

Files drivers/imx/usdhc/

#### NXP i.MX 8 platform port

Mail Peng Fan <peng.fan@nxp.com>

GitHub ID MrVan

Files docs/plat/imx8.rst

Files plat/imx/

#### NXP i.MX8M platform port

Mail Jacky Bai <ping.bai@nxp.com>

GitHub ID JackyBai

Files docs/plat/imx8m.rst

Files plat/imx/imx8m/

#### NXP QorlQ Layerscape common code for platform ports

Mail Pankaj Gupta <pankaj.gupta@nxp.com>

GitHub ID pangupta

Files docs/plat/nxp/

Files plat/nxp/

Files drivers/nxp/

Files tools/nxp/

#### NXP SoC Part LX2160A and its platform port

Mail Pankaj Gupta <pankaj.gupta@nxp.com>

GitHub ID pangupta

Files plat/nxp/soc-lx2160a

Files plat/nxp/soc-lx2160a/lx2162aqds

Files plat/nxp/soc-lx2160a/lx2160aqds

Files plat/nxp/soc-lx2160a/lx2160ardb

#### **QEMU** platform port

Mail Jens Wiklander < jens.wiklander@linaro.org>

GitHub ID jenswi-linaro

Files docs/plat/qemu.rst

Files plat/qemu/

#### QTI platform port

Mail Saurabh Gorecha <sgorecha@codeaurora.org>

GitHub ID sgorecha

Mail Lachit Patel | Codeaurora.org>

GitHub ID lachitp

Mail Sreevyshanavi Kare <skare@codeaurora.org>

GitHub ID sreekare

Mail QTI TF Maintainers <qti.trustedfirmware.maintainers@codeaurora.org>

Files docs/plat/qti.rst

Files plat/qti/

#### Raspberry Pi 3 platform port

Mail Ying-Chun Liu (PaulLiu) <paul.liu@linaro.org>

GitHub ID grandpaul

Files docs/plat/rpi3.rst

Files plat/rpi/rpi3/

Files plat/rpi/common/

Files drivers/rpi3/

Files include/drivers/rpi3/

#### Raspberry Pi 4 platform port

Mail Andre Przywara <andre.przywara@arm.com>

GitHub ID Andre-ARM

Files docs/plat/rpi4.rst

Files plat/rpi/rpi4/

Files plat/rpi/common/

Files drivers/rpi3/

Files include/drivers/rpi3/

#### Renesas rcar-gen3 platform port

Mail Jorge Ramirez-Ortiz < jramirez@baylibre.com>

GitHub ID 1dts

Mail Marek Vasut <marek.vasut@gmail.com>

GitHub ID marex

Files docs/plat/rcar-gen3.rst

Files plat/renesas/common

Files plat/renesas/rcar

Files drivers/renesas/common

Files drivers/renesas/rcar

Files tools/renesas/rcar\_layout\_create

#### Renesas RZ/G2 platform port

Mail Biju Das <br/> <br/>biju.das.jz@bp.renesas.com>

GitHub ID bijucdas

Mail Marek Vasut <marek.vasut@gmail.com>

GitHub ID marex

Mail Lad Prabhakar <prabhakar.mahadev-lad.rj@bp.renesas.com>

GitHub ID prabhakarlad

Files docs/plat/rz-g2.rst

Files plat/renesas/common

**Files** plat/renesas/rzg

Files drivers/renesas/common

Files drivers/renesas/rzg

Files tools/renesas/rzg\_layout\_create

#### RockChip platform port

Mail Tony Xie <tony.xie@rock-chips.com>

GitHub ID TonyXie06

GitHub ID rockchip-linux

Mail Heiko Stuebner <heiko@sntech.de>

GitHub ID mmind

Mail Julius Werner < jwerner@chromium.org>

GitHub ID jwerner-chromium

Files plat/rockchip/

#### STM32MP1 platform port

Mail Yann Gautier < yann.gautier@st.com>

GitHub ID Yann-lms

Files docs/plat/stm32mp1.rst

Files drivers/st/

Files fdts/stm32\*

Files include/drivers/st/

Files include/dt-bindings/\*/stm32\*

Files plat/st/

Files tools/stm32image/

#### Synquacer platform port

Mail Sumit Garg <sumit.garg@linaro.org>

**GitHub ID** b49020

Files docs/plat/synquacer.rst

Files plat/socionext/synquacer/

#### **Texas Instruments platform port**

Mail Nishanth Menon <nm@ti.com>

GitHub ID nmenon

Files docs/plat/ti-k3.rst

Files plat/ti/

#### **UniPhier platform port**

Mail Orphan

Files docs/plat/socionext-uniphier.rst

Files plat/socionext/uniphier/

#### Xilinx platform port

Mail Michal Simek <michal.simek@xilinx.com>

GitHub ID michalsimek

Mail Venkatesh Yadav Abbarapu <venkatesh.abbarapu@xilinx.com>

GitHub ID venkatesh

Files docs/plat/xilinx-zynqmp.rst

Files plat/xilinx/

#### **Secure Payloads and Dispatchers**

#### **OP-TEE dispatcher**

Mail Jens Wiklander < jens.wiklander@linaro.org>

GitHub ID jenswi-linaro

Files docs/components/spd/optee-dispatcher.rst

Files services/spd/opteed/

#### TLK/Trusty secure payloads

Mail Varun Wadekar < vwadekar@nvidia.com>

GitHub ID vwadekar

Files docs/components/spd/tlk-dispatcher.rst

Files docs/components/spd/trusty-dispatcher.rst

Files include/bl32/payloads/tlk.h

Files services/spd/tlkd/

Files services/spd/trusty/

#### **Test Secure Payload (TSP)**

Mail Manish Badarkhe <manish.badarkhe@arm.com>

GitHub ID ManishVB-Arm

Files bl32/tsp/

**Files** services/spd/tspd/

#### **Tools**

#### **Fiptool**

Mail Joao Alves < Joao. Alves @ arm.com>

GitHub ID J-Alves

Files tools/fiptool/

#### Cert create tool

Mail Sandrine Bailleux <sandrine.bailleux@arm.com>

GitHub ID sandrine-bailleux-arm

Files tools/cert\_create/

#### Encrypt\_fw tool

Mail Sumit Garg <sumit.garg@linaro.org>

GitHub ID b49020

Files tools/encrypt\_fw/

#### **Sptool**

Mail Manish Pandey <manish.pandey2@arm.com>

GitHub ID manish-pandey-arm

Files tools/sptool/

#### **Build system**

Mail Manish Pandey <manish.pandey2@arm.com>

GitHub ID manish-pandey-arm

Files Makefile

Files make\_helpers/

#### **Threat Model**

Mail Zelalem Aweke <Zelalem.Aweke@arm.com>

GitHub ID zelalem-aweke

Mail Sandrine Bailleux <sandrine.bailleux@arm.com>

GitHub ID sandrine-bailleux-arm

Mail Joanna Farley <joanna.farley@arm.com>

GitHub ID joannafarley-arm

Mail Raghu Krishnamurthy <raghu.ncstate@icloud.com>

GitHub ID raghuncstate

Mail Varun Wadekar < vwadekar@nvidia.com>

GitHub ID vwadekar

Files docs/threat\_model/

#### **Conventional Changelog Extensions**

Mail Chris Kay <chris.kay@arm.com>

GitHub ID CJKay

Files tools/conventional-changelog-tf-a

## 1.4 Support & Contact

We welcome any feedback on TF-A and there are several methods for providing it or for obtaining support.

**Warning:** If you think you have found a security vulnerability, please report this using the process defined in the *Security Handling* document.

## 1.4.1 Mailing Lists

Public mailing lists for TF-A and the wider Trusted Firmware project are hosted on TrustedFirmware.org. The mailing lists can be used for general enquiries, enhancement requests and issue reports, or to follow and participate in technical or organizational discussions around the project. These discussions include design proposals, advance notice of changes and upcoming events.

The relevant lists for the TF-A project are:

- TF-A development

- TF-A-Tests development

You can see a summary of all the lists on the TrustedFirmware.org website.

#### 1.4.2 Open Tech Forum Call

Every other week, we organize a call with all interested TF-A contributors. Anyone is welcome to join. This is an opportunity to discuss any technical topic within the community. More details can be found here.

#### 1.4.3 Issue Tracker

Bug reports may be filed on the issue tracker on the TrustedFirmware.org website. Using this tracker gives everyone visibility of the known issues in TF-A.

#### 1.4.4 Arm Licensees

Arm licensees have an additional support conduit - they may contact Arm directly via their partner managers.

Copyright (c) 2019-2020, Arm Limited. All rights reserved.

## 1.5 Contributor Acknowledgements

**Note:** This file is only relevant for legacy contributions, to acknowledge the specific contributors referred to in "Arm Limited and Contributors" copyright notices. As contributors are now encouraged to put their name or company name directly into the copyright notices, this file is not relevant for new contributions. See the *License* document for the correct template to use for new contributions.

· Linaro Limited

- Marvell International Ltd.

- NVIDIA Corporation

- NXP Semiconductors

- Socionext Inc.

- STMicroelectronics

- Xilinx, Inc.

Copyright (c) 2019, Arm Limited. All rights reserved.

**CHAPTER**

**TWO**

## **GETTING STARTED**

## 2.1 Prerequisites

This document describes the software requirements for building *TF-A* for AArch32 and AArch64 target platforms.

It may possible to build *TF-A* with combinations of software packages that are different from those listed below, however only the software described in this document can be officially supported.

#### 2.1.1 Build Host

TF-A can be built using either a Linux or a Windows machine as the build host.

A relatively recent Linux distribution is recommended for building *TF-A*. We have performed tests using Ubuntu 16.04 LTS (64-bit) but other distributions should also work fine as a base, provided that the necessary tools and libraries can be installed.

#### 2.1.2 Toolchain

TF-A can be built with any of the following cross-compiler toolchains that target the Armv7-A or Armv8-A architectures:

- GCC >= 10.3-2021.07 (from the Arm Developer website)

- Clang >= 4.0

- Arm Compiler >= 6.0

In addition, a native compiler is required to build the supporting tools.

**Note:** The software has also been built on Windows 7 Enterprise SP1, using CMD.EXE, Cygwin, and Msys (MinGW) shells, using version 5.3.1 of the GNU toolchain.

Note: For instructions on how to select the cross compiler refer to Performing an Initial Build.

#### 2.1.3 Software and Libraries

The following tools are required to obtain and build *TF-A*:

- An appropriate toolchain (see *Toolchain*)

- · GNU Make

- Git

The following libraries must be available to build one or more components or supporting tools:

• OpenSSL >= 1.0.1

Required to build the cert create tool.

The following libraries are required for Trusted Board Boot support:

• mbed TLS == 2.26.0 (tag: mbedtls-2.26.0)

These tools are optional:

• Device Tree Compiler (DTC) >= 1.4.6

Needed if you want to rebuild the provided Flattened Device Tree (FDT) source files (.dts files). DTC is available for Linux through the package repositories of most distributions.

• Arm Development Studio 5 (DS-5)

The standard software package used for debugging software on Arm development platforms and *FVP* models.

• Node.js >= 16

Highly recommended, and necessary in order to install and use the packaged Git hooks and helper tools. Without these tools you will need to rely on the CI for feedback on commit message conformance.

#### Package Installation (Linux)

If you are using the recommended Ubuntu distribution then you can install the required packages with the following command:

```

sudo apt install build-essential git libssl-dev

```

The optional packages can be installed using:

```

sudo apt install device-tree-compiler

```

Additionally, to install an up-to-date version of Node.js, you can use the Node Version Manager to install a version of your choosing (we recommend 16, but later LTS versions might offer a more stable experience):

```

curl -o- https://raw.githubusercontent.com/nvm-sh/nvm/v0.39.0/install.sh | "$SHELL"

exec "$SHELL" -ic "nvm install 16; exec $SHELL"

```

#### 2.1.4 Supporting Files

TF-A has been tested with pre-built binaries and file systems from Linaro Release 20.01. Alternatively, you can build the binaries from source using instructions in *Performing an Initial Build*.

#### 2.1.5 Getting the TF-A Source

Source code for *TF-A* is maintained in a Git repository hosted on TrustedFirmware.org. To clone this repository from the server, run the following in your shell:

```

git clone "https://review.trustedfirmware.org/TF-A/trusted-firmware-a"

```

#### **Additional Steps for Contributors**

If you are planning on contributing back to TF-A, there are some things you'll want to know.

TF-A is hosted by a Gerrit Code Review server. Gerrit requires that all commits include a Change-Id footer, and this footer is typically automatically generated by a Git hook installed by you, the developer.

If you have Node.js installed already, you can automatically install this hook, along with any additional hooks and Javascript-based tooling that we use, by running from within your newly-cloned repository:

```

npm install --no-save

```

If you have opted **not** to install Node.js, you can install the Gerrit hook manually by running:

```

curl -Lo $(git rev-parse --git-dir)/hooks/commit-msg https://review.trustedfirmware.org/

-tools/hooks/commit-msg

chmod +x $(git rev-parse --git-dir)/hooks/commit-msg

```

You can read more about Git hooks in the githooks page of the Git documentation, available here.

Copyright (c) 2021, Arm Limited. All rights reserved.

## 2.2 Building Documentation

To create a rendered copy of this documentation locally you can use the Sphinx tool to build and package the plain-text documents into HTML-formatted pages.

If you are building the documentation for the first time then you will need to check that you have the required software packages, as described in the *Prerequisites* section that follows.

**Note:** An online copy of the documentation is available at https://www.trustedfirmware.org/docs/tf-a, if you want to view a rendered copy without doing a local build.

#### 2.2.1 Prerequisites

For building a local copy of the *TF-A* documentation you will need, at minimum:

- Python 3 (3.5 or later)

- PlantUML (1.2017.15 or later)

Optionally, the Dia application can be installed if you need to edit existing .dia diagram files, or create new ones.

You must also install the Python modules that are specified in the requirements.txt file in the root of the docs directory. These modules can be installed using pip3 (the Python Package Installer). Passing this requirements file as an argument to pip3 automatically installs the specific module versions required by *TF-A*.

An example set of installation commands for Ubuntu 18.04 LTS follows, assuming that the working directory is docs:

```

sudo apt install python3 python3-pip plantuml [dia]

pip3 install [--user] -r requirements.txt

```

**Note:** Several other modules will be installed as dependencies. Please review the list to ensure that there will be no conflicts with other modules already installed in your environment.

Passing the optional --user argument to pip3 will install the Python packages only for the current user. Omitting this argument will attempt to install the packages globally and this will likely require the command to be run as root or using sudo.

**Note:** More advanced usage instructions for *pip* are beyond the scope of this document but you can refer to the pip homepage for detailed guides.

## 2.2.2 Building rendered documentation

Documents can be built into HTML-formatted pages from project root directory by running the following command.

make doc

Output from the build process will be placed in:

docs/build/html

We also support building documentation in other formats. From the docs directory of the project, run the following command to see the supported formats. It is important to note that you will not get the correct result if the command is run from the project root directory, as that would invoke the top-level Makefile for *TF-A* itself.

make help

## 2.2.3 Building rendered documentation from a container

There may be cases where you can not either install or upgrade required dependencies to generate the documents, so in this case, one way to create the documentation is through a docker container. The first step is to check if docker is installed in your host, otherwise check main docker page for installation instructions. Once installed, run the following script from project root directory

```

docker run --rm -v $PWD:/TF sphinxdoc/sphinx \

bash -c 'cd /TF && \

pip3 install plantuml -r ./docs/requirements.txt && make doc'

```

The above command fetches the sphinxdoc/sphinx container from docker hub, launches the container, installs documentation requirements and finally creates the documentation. Once done, exit the container and output from the build process will be placed in:

docs/build/html

Copyright (c) 2019, Arm Limited. All rights reserved.

## 2.3 Building Supporting Tools

#### 2.3.1 Building and using the FIP tool

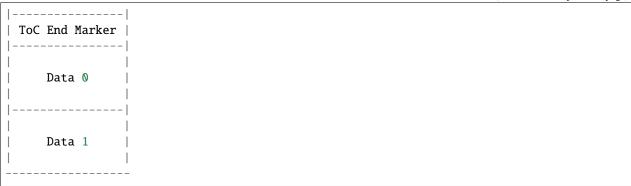

Firmware Image Package (FIP) is a packaging format used by TF-A to package firmware images in a single binary. The number and type of images that should be packed in a FIP is platform specific and may include TF-A images and other firmware images required by the platform. For example, most platforms require a BL33 image which corresponds to the normal world bootloader (e.g. UEFI or U-Boot).

The TF-A build system provides the make target fip to create a FIP file for the specified platform using the FIP creation tool included in the TF-A project. Examples below show how to build a FIP file for FVP, packaging TF-A and BL33 images.

For AArch64:

```

make PLAT=fvp BL33=<path-to>/bl33.bin fip

```

For AArch32:

```

make PLAT=fvp ARCH=aarch32 AARCH32_SP=sp_min BL33=<path-to>/bl33.bin fip

```

The resulting FIP may be found in:

```

build/fvp/<build-type>/fip.bin

```

For advanced operations on FIP files, it is also possible to independently build the tool and create or modify FIPs using this tool. To do this, follow these steps:

It is recommended to remove old artifacts before building the tool:

```

make -C tools/fiptool clean

```

Build the tool:

```

make [DEBUG=1] [V=1] fiptool

```

The tool binary can be located in:

```

./tools/fiptool/fiptool

```

Invoking the tool with help will print a help message with all available options.

Example 1: create a new Firmware package fip.bin that contains BL2 and BL31:

```

./tools/fiptool/fiptool create \

--tb-fw build/<platform>/<build-type>/bl2.bin \

--soc-fw build/<platform>/<build-type>/bl31.bin \

fip.bin

```

Example 2: view the contents of an existing Firmware package:

```

./tools/fiptool/fiptool info <path-to>/fip.bin

```

Example 3: update the entries of an existing Firmware package:

```

# Change the BL2 from Debug to Release version

./tools/fiptool/fiptool update \

--tb-fw build/<platform>/release/bl2.bin \

build/<platform>/debug/fip.bin

```

Example 4: unpack all entries from an existing Firmware package:

```

# Images will be unpacked to the working directory

./tools/fiptool unpack <path-to>/fip.bin

```

Example 5: remove an entry from an existing Firmware package:

```

./tools/fiptool remove \

--tb-fw build/<platform>/debug/fip.bin

```

Note that if the destination FIP file exists, the create, update and remove operations will automatically overwrite it.

The unpack operation will fail if the images already exist at the destination. In that case, use -f or -force to continue.

More information about FIP can be found in the Firmware Design document.

## 2.3.2 Building the Certificate Generation Tool

The cert\_create tool is built as part of the TF-A build process when the fip make target is specified and TBB is enabled (as described in the previous section), but it can also be built separately with the following command:

```

make PLAT=<platform> [DEBUG=1] [V=1] certtool

```

For platforms that require their own IDs in certificate files, the generic 'cert\_create' tool can be built with the following command. Note that the target platform must define its IDs within a platform\_oid.h header file for the build to succeed.

```

make PLAT=<platform> USE_TBBR_DEFS=0 [DEBUG=1] [V=1] certtool

```

DEBUG=1 builds the tool in debug mode. V=1 makes the build process more verbose. The following command should be used to obtain help about the tool:

```

./tools/cert_create/cert_create -h

```

## **Building the Firmware Encryption Tool**

The encrypt\_fw tool is built as part of the TF-A build process when the fip make target is specified, DECRYP-TION\_SUPPORT and TBB are enabled, but it can also be built separately with the following command:

```

make PLAT=<platform> [DEBUG=1] [V=1] enctool

```

DEBUG=1 builds the tool in debug mode. V=1 makes the build process more verbose. The following command should be used to obtain help about the tool:

```

./tools/encrypt_fw/encrypt_fw -h

```

Note that the enctool in its current implementation only supports encryption key to be provided in plain format. A typical implementation can very well extend this tool to support custom techniques to protect encryption key.

Also, a user may choose to provide encryption key or nonce as an input file via using cat <filename> instead of a hex string.

Copyright (c) 2019, Arm Limited. All rights reserved.

# 2.4 Performing an Initial Build

Before building TF-A, the environment variable CROSS\_COMPILE must point to the Linaro cross compiler.

For AArch64:

```

export CROSS_COMPILE=<path-to-aarch64-gcc>/bin/aarch64-none-elf-

```

For AArch32:

```

export CROSS_COMPILE=<path-to-aarch32-gcc>/bin/arm-none-eabi-

```

It is possible to build TF-A using Clang or Arm Compiler 6. To do so CC needs to point to the clang or armclang binary, which will also select the clang or armclang assembler. Be aware that for Arm Compiler, the GNU linker is used by default. However for Clang LLVM linker (LLD) is used by default. In case of being needed the linker can be overridden using the LD variable. LLVM linker (LLD) version 9 is known to work with TF-A.

In both cases CROSS\_COMPILE should be set as described above.

Arm Compiler 6 will be selected when the base name of the path assigned to CC matches the string 'armclang'.

For AArch64 using Arm Compiler 6:

```

export CROSS_COMPILE=<path-to-aarch64-gcc>/bin/aarch64-none-elf-make CC=<path-to-armclang>/bin/armclang PLAT=<platform> all

```

Clang will be selected when the base name of the path assigned to CC contains the string 'clang'. This is to allow both clang and clang-X.Y to work.

For AArch64 using clang:

```

export CROSS_COMPILE=<path-to-aarch64-gcc>/bin/aarch64-none-elf-

make CC=<path-to-clang>/bin/clang PLAT=<platform> all

```

• Change to the root directory of the TF-A source tree and build.

For AArch64:

```

make PLAT=<platform> all

```

For AArch32:

```

make PLAT=<platform> ARCH=aarch32 AARCH32_SP=sp_min all

```

#### Notes:

- If PLAT is not specified, fvp is assumed by default. See the *Build Options* document for more information on available build options.

- (AArch32 only) Currently only PLAT=fvp is supported.

- (AArch32 only) AARCH32\_SP is the AArch32 EL3 Runtime Software and it corresponds to the BL32 image. A minimal AARCH32\_SP, sp\_min, is provided by TF-A to demonstrate how PSCI Library can be integrated with an AArch32 EL3 Runtime Software. Some AArch32 EL3 Runtime Software may include other runtime services, for example Trusted OS services. A guide to integrate PSCI library with AArch32 EL3 Runtime Software can be found at PSCI Library Integration guide for Armv8-A AArch32 systems.

- (AArch64 only) The TSP (Test Secure Payload), corresponding to the BL32 image, is not compiled in by default. Refer to the *Test Secure Payload (TSP) and Dispatcher (TSPD)* document for details on building the TSP.

- By default this produces a release version of the build. To produce a debug version instead, refer to the "Debugging options" section below.

- The build process creates products in a build directory tree, building the objects and binaries for each boot loader stage in separate sub-directories. The following boot loader binary files are created from the corresponding ELF files:

- \* build/<platform>/<build-type>/bl1.bin

- \* build/<platform>/<build-type>/bl2.bin

- \* build/<platform>/<build-type>/bl31.bin (AArch64 only)

- \* build/<platform>/<build-type>/bl32.bin (mandatory for AArch32)

where <platform> is the name of the chosen platform and <build-type> is either debug or release. The actual number of images might differ depending on the platform.

• Build products for a specific build variant can be removed using:

```

make DEBUG=<D> PLAT=<platform> clean

```

... where <D> is 0 or 1, as specified when building.

The build tree can be removed completely using:

```

make realclean

```

Copyright (c) 2020, Arm Limited. All rights reserved.

# 2.5 Build Options

The TF-A build system supports the following build options. Unless mentioned otherwise, these options are expected to be specified at the build command line and are not to be modified in any component makefiles. Note that the build system doesn't track dependency for build options. Therefore, if any of the build options are changed from a previous build, a clean build must be performed.

## 2.5.1 Common build options

- AARCH32\_INSTRUCTION\_SET: Choose the AArch32 instruction set that the compiler should use. Valid values are T32 and A32. It defaults to T32 due to code having a smaller resulting size.

- AARCH32\_SP: Choose the AArch32 Secure Payload component to be built as as the BL32 image when ARCH=aarch32. The value should be the path to the directory containing the SP source, relative to the bl32/; the directory is expected to contain a makefile called <aarch32\_sp-value>.mk.

- AMU\_RESTRICT\_COUNTERS: Register reads to the group 1 counters will return zero at all but the highest implemented exception level. Reads from the memory mapped view are unaffected by this control.

- ARCH: Choose the target build architecture for TF-A. It can take either aarch64 or aarch32 as values. By default, it is defined to aarch64.

- ARM\_ARCH\_FEATURE: Optional Arm Architecture build option which specifies one or more feature modifiers. This option has the form [no]feature+... and defaults to none. It translates into compiler option -march=armvX[.Y]-a+[no]feature+.... See compiler's documentation for the list of supported feature modifiers.

- ARM\_ARCH\_MAJOR: The major version of Arm Architecture to target when compiling TF-A. Its value must be numeric, and defaults to 8. See also, *Armv8 Architecture Extensions* and *Armv7 Architecture Extensions* in *Firmware Design*.

- ARM\_ARCH\_MINOR: The minor version of Arm Architecture to target when compiling TF-A. Its value must be a numeric, and defaults to 0. See also, *Armv8 Architecture Extensions* in *Firmware Design*.

- BL2: This is an optional build option which specifies the path to BL2 image for the fip target. In this case, the BL2 in the TF-A will not be built.

- BL2U: This is an optional build option which specifies the path to BL2U image. In this case, the BL2U in TF-A will not be built.

- BL2\_AT\_EL3: This is an optional build option that enables the use of BL2 at EL3 execution level.

- BL2\_ENABLE\_SP\_LOAD: Boolean option to enable loading SP packages from the FIP. Automatically enabled if SP\_LAYOUT\_FILE is provided.

- BL2\_IN\_XIP\_MEM: In some use-cases BL2 will be stored in eXecute In Place (XIP) memory, like BL1. In these use-cases, it is necessary to initialize the RW sections in RAM, while leaving the RO sections in place. This option enable this use-case. For now, this option is only supported when BL2\_AT\_EL3 is set to '1'.

- BL31: This is an optional build option which specifies the path to BL31 image for the fip target. In this case, the BL31 in TF-A will not be built.

- BL31\_KEY: This option is used when GENERATE\_COT=1. It specifies the file that contains the BL31 private key in PEM format. If SAVE\_KEYS=1, this file name will be used to save the key.

- BL32: This is an optional build option which specifies the path to BL32 image for the fip target. In this case, the BL32 in TF-A will not be built.

- BL32\_EXTRA1: This is an optional build option which specifies the path to Trusted OS Extra1 image for the fip target.

2.5. Build Options 35

- BL32\_EXTRA2: This is an optional build option which specifies the path to Trusted OS Extra2 image for the fip target.

- BL32\_KEY: This option is used when GENERATE\_COT=1. It specifies the file that contains the BL32 private key in PEM format. If SAVE\_KEYS=1, this file name will be used to save the key.

- BL33: Path to BL33 image in the host file system. This is mandatory for fip target in case TF-A BL2 is used.

- BL33\_KEY: This option is used when GENERATE\_COT=1. It specifies the file that contains the BL33 private key in PEM format. If SAVE\_KEYS=1, this file name will be used to save the key.

- BRANCH\_PROTECTION: Numeric value to enable ARMv8.3 Pointer Authentication and ARMv8.5 Branch Target Identification support for TF-A BL images themselves. If enabled, it is needed to use a compiler that supports the option -mbranch-protection. Selects the branch protection features to use:

- 0: Default value turns off all types of branch protection

- 1: Enables all types of branch protection features

- 2: Return address signing to its standard level

- 3: Extend the signing to include leaf functions

- 4: Turn on branch target identification mechanism

The table below summarizes BRANCH\_PROTECTION values, GCC compilation options and resulting PAuth/BTI features.

| Value | GCC option   | PAuth | BTI |

|-------|--------------|-------|-----|

| 0     | none         | N     | N   |

| 1     | standard     | Y     | Y   |

| 2     | pac-ret      | Y     | N   |

| 3     | pac-ret+leaf | Y     | N   |

| 4     | bti          | N     | Y   |

This option defaults to 0. Note that Pointer Authentication is enabled for Non-secure world irrespective of the value of this option if the CPU supports it.

- BUILD\_MESSAGE\_TIMESTAMP: String used to identify the time and date of the compilation of each build. It must be set to a C string (including quotes where applicable). Defaults to a string that contains the time and date of the compilation.

- BUILD\_STRING: Input string for VERSION\_STRING, which allows the TF-A build to be uniquely identified. Defaults to the current git commit id.

- BUILD\_BASE: Output directory for the build. Defaults to ./build

- CFLAGS: Extra user options appended on the compiler's command line in addition to the options set by the build system.

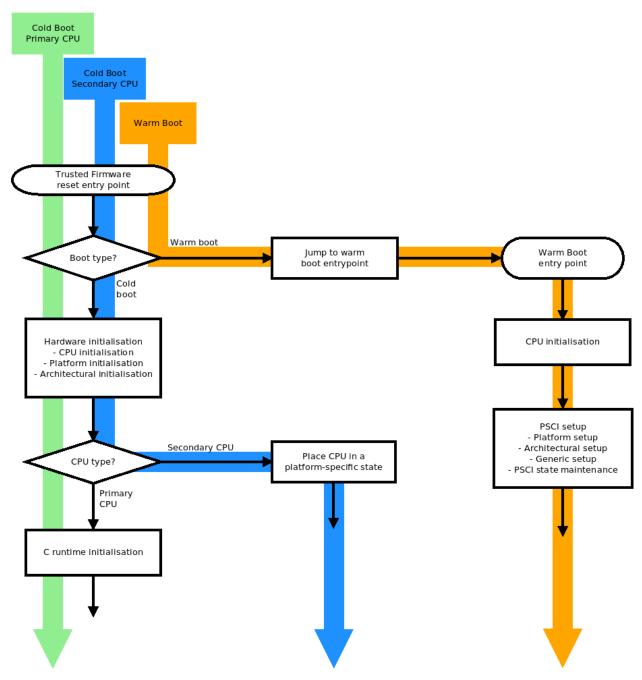

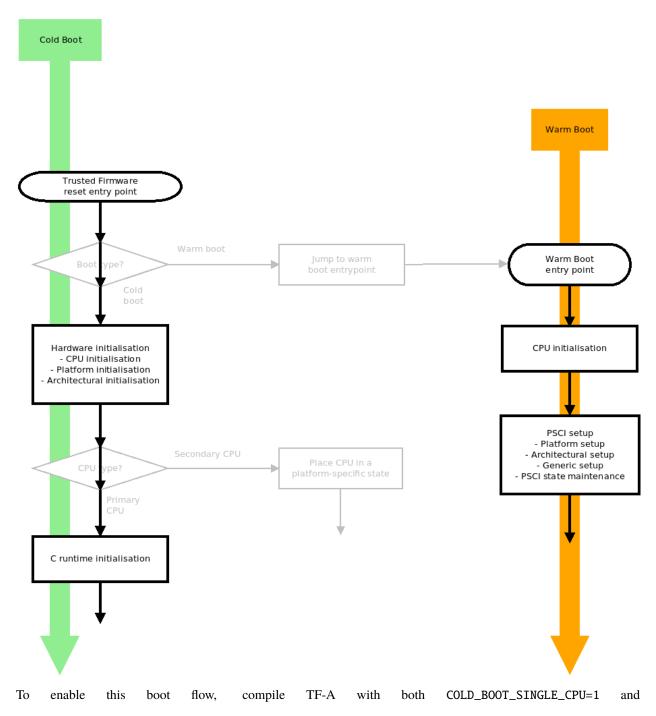

- COLD\_BOOT\_SINGLE\_CPU: This option indicates whether the platform may release several CPUs out of reset. It can take either 0 (several CPUs may be brought up) or 1 (only one CPU will ever be brought up during cold reset). Default is 0. If the platform always brings up a single CPU, there is no need to distinguish between primary and secondary CPUs and the boot path can be optimised. The plat\_is\_my\_cpu\_primary() and plat\_secondary\_cold\_boot\_setup() platform porting interfaces do not need to be implemented in this case.

- COT: When Trusted Boot is enabled, selects the desired chain of trust. Defaults to tbbr.

- CRASH\_REPORTING: A non-zero value enables a console dump of processor register state when an unexpected

exception occurs during execution of BL31. This option defaults to the value of DEBUG i.e. by default this is

only enabled for a debug build of the firmware.

- CREATE\_KEYS: This option is used when GENERATE\_COT=1. It tells the certificate generation tool to create new keys in case no valid keys are present or specified. Allowed options are '0' or '1'. Default is '1'.

- CTX\_INCLUDE\_AARCH32\_REGS: Boolean option that, when set to 1, will cause the AArch32 system registers to be included when saving and restoring the CPU context. The option must be set to 0 for AArch64-only platforms (that is on hardware that does not implement AArch32, or at least not at EL1 and higher ELs). Default value is

- CTX\_INCLUDE\_EL2\_REGS: This boolean option provides context save/restore operations when entering/exiting an EL2 execution context. This is of primary interest when Armv8.4-SecEL2 extension is implemented. Default is 0 (disabled). This option must be equal to 1 (enabled) when SPD=spmd and SPMD\_SPM\_AT\_SEL2 is set.

- CTX\_INCLUDE\_FPREGS: Boolean option that, when set to 1, will cause the FP registers to be included when saving and restoring the CPU context. Default is 0.

- CTX\_INCLUDE\_NEVE\_REGS: Boolean option that, when set to 1, will cause the Armv8.4-NV registers to be saved/restored when entering/exiting an EL2 execution context. Default value is 0.

- CTX\_INCLUDE\_PAUTH\_REGS: Boolean option that, when set to 1, enables Pointer Authentication for Secure world. This will cause the ARMv8.3-PAuth registers to be included when saving and restoring the CPU context as part of world switch. Default value is 0. Note that Pointer Authentication is enabled for Non-secure world irrespective of the value of this flag if the CPU supports it.

- DEBUG: Chooses between a debug and release build. It can take either 0 (release) or 1 (debug) as values. 0 is the default.

- DECRYPTION\_SUPPORT: This build flag enables the user to select the authenticated decryption algorithm to be used to decrypt firmware/s during boot. It accepts 2 values: aes\_gcm and none. The default value of this flag is none to disable firmware decryption which is an optional feature as per TBBR.

- DISABLE\_BIN\_GENERATION: Boolean option to disable the generation of the binary image. If set to 1, then only the ELF image is built. 0 is the default.

- DISABLE\_MTPMU: Boolean option to disable FEAT\_MTPMU if implemented (Armv8.6 onwards). Its default value is 0 to keep consistency with platforms that do not implement FEAT\_MTPMU. For more information on FEAT MTPMU, check the latest Arm ARM.

- DYN\_DISABLE\_AUTH: Provides the capability to dynamically disable Trusted Board Boot authentication at runtime. This option is meant to be enabled only for development platforms. TRUSTED\_BOARD\_BOOT flag must be set if this flag has to be enabled. 0 is the default.

- E: Boolean option to make warnings into errors. Default is 1.

- EL3\_PAYLOAD\_BASE: This option enables booting an EL3 payload instead of the normal boot flow. It must specify the entry point address of the EL3 payload. Please refer to the "Booting an EL3 payload" section for more details.

- ENABLE\_AMU: Boolean option to enable Activity Monitor Unit extensions. This is an optional architectural feature available on v8.4 onwards. Some v8.2 implementations also implement an AMU and this option can be used to enable this feature on those systems as well. Default is 0.

- ENABLE\_AMU\_AUXILIARY\_COUNTERS: Enables support for AMU auxiliary counters (also known as group 1 counters). These are implementation-defined counters, and as such require additional platform configuration. Default is 0.

- ENABLE\_AMU\_FCONF: Enables configuration of the AMU through FCONF, which allows platforms with auxiliary

counters to describe them via the HW\_CONFIG device tree blob. Default is 0.

- ENABLE\_ASSERTIONS: This option controls whether or not calls to assert() are compiled out. For debug builds, this option defaults to 1, and calls to assert() are left in place. For release builds, this option defaults to 0 and calls to assert() function are compiled out. This option can be set independently of DEBUG. It can also be used to hide any auxiliary code that is only required for the assertion and does not fit in the assertion itself.

2.5. Build Options 37

- ENABLE\_BACKTRACE: This option controls whether to enable backtrace dumps or not. It is supported in both AArch64 and AArch32. However, in AArch32 the format of the frame records are not defined in the AAPCS and they are defined by the implementation. This implementation of backtrace only supports the format used by GCC when T32 interworking is disabled. For this reason enabling this option in AArch32 will force the compiler to only generate A32 code. This option is enabled by default only in AArch64 debug builds, but this behaviour can be overridden in each platform's Makefile or in the build command line.

- ENABLE\_FEAT\_HCX: This option sets the bit SCR\_EL3.HXEn in EL3 to allow access to HCRX\_EL2 (extended hypervisor control register) from EL2 as well as adding HCRX\_EL2 to the EL2 context save/restore operations.

- ENABLE\_LTO: Boolean option to enable Link Time Optimization (LTO) support in GCC for TF-A. This option is currently only supported for AArch64. Default is 0.

- ENABLE\_MPAM\_FOR\_LOWER\_ELS: Boolean option to enable lower ELs to use MPAM feature. MPAM is an optional Armv8.4 extension that enables various memory system components and resources to define partitions; software running at various ELs can assign themselves to desired partition to control their performance aspects.

- When this option is set to 1, EL3 allows lower ELs to access their own MPAM registers without trapping into EL3. This option doesn't make use of partitioning in EL3, however. Platform initialisation code should configure and use partitions in EL3 as required. This option defaults to 0.

- ENABLE\_MPMM: Boolean option to enable support for the Maximum Power Mitigation Mechanism supported by certain Arm cores, which allows the SoC firmware to detect and limit high activity events to assist in SoC processor power domain dynamic power budgeting and limit the triggering of whole-rail (i.e. clock chopping) responses to overcurrent conditions. Defaults to 0.

- ENABLE\_MPMM\_FCONF: Enables configuration of MPMM through FCONF, which allows platforms with cores supporting MPMM to describe them via the HW\_CONFIG device tree blob. Default is 0.

- ENABLE\_PIE: Boolean option to enable Position Independent Executable(PIE) support within generic code in TF-A. This option is currently only supported in BL2\_AT\_EL3, BL31, and BL32 (TSP) for AARCH64 binaries, and in BL32 (SP\_min) for AARCH32. Default is 0.

- ENABLE\_PMF: Boolean option to enable support for optional Performance Measurement Framework(PMF). Default is 0.

- ENABLE\_PSCI\_STAT: Boolean option to enable support for optional PSCI functions PSCI\_STAT\_RESIDENCY and PSCI\_STAT\_COUNT. Default is 0. In the absence of an alternate stat collection backend, ENABLE\_PMF must be enabled. If ENABLE\_PMF is set, the residency statistics are tracked in software.

- ENABLE\_RME: Boolean option to enable support for the ARMv9 Realm Management Extension. Default value is 0. This is currently an experimental feature.

- ENABLE\_RUNTIME\_INSTRUMENTATION: Boolean option to enable runtime instrumentation which injects timestamp collection points into TF-A to allow runtime performance to be measured. Currently, only PSCI is instrumented. Enabling this option enables the ENABLE\_PMF build option as well. Default is 0.

- ENABLE\_SME\_FOR\_NS: Boolean option to enable Scalable Matrix Extension (SME), SVE, and FPU/SIMD for the non-secure world only. These features share registers so are enabled together. Using this option without ENABLE\_SME\_FOR\_SWD=1 will cause SME, SVE, and FPU/SIMD instructions in secure world to trap to EL3. SME is an optional architectural feature for AArch64 and TF-A support is experimental. At this time, this build option cannot be used on systems that have SPD=spmd/SPM\_MM or ENABLE\_RME, and attempting to build with these options will fail. Default is 0.

- ENABLE\_SME\_FOR\_SWD: Boolean option to enable the Scalable Matrix Extension for secure world use along with SVE and FPU/SIMD, ENABLE\_SME\_FOR\_NS must also be set to use this. If enabling this, the secure world MUST handle context switching for SME, SVE, and FPU/SIMD registers to ensure that no data is leaked to non-secure world. This is experimental. Default is 0.

- ENABLE\_SPE\_FOR\_LOWER\_ELS: Boolean option to enable Statistical Profiling extensions. This is an optional architectural feature for AArch64. The default is 1 but is automatically disabled when the target architecture is

AArch32.

- ENABLE\_SVE\_FOR\_NS: Boolean option to enable Scalable Vector Extension (SVE) for the Non-secure world only. SVE is an optional architectural feature for AArch64. Note that when SVE is enabled for the Non-secure world, access to SIMD and floating-point functionality from the Secure world is disabled by default and controlled with ENABLE\_SVE\_FOR\_SWD. This is to avoid corruption of the Non-secure world data in the Z-registers which are aliased by the SIMD and FP registers. The build option is not compatible with the CTX\_INCLUDE\_FPREGS build option, and will raise an assert on platforms where SVE is implemented and ENABLE\_SVE\_FOR\_NS set to 1. The default is 1 but is automatically disabled when ENABLE\_SME\_FOR\_NS=1 since SME encompasses SVE. At this time, this build option cannot be used on systems that have SPM\_MM enabled.

- ENABLE\_SVE\_FOR\_SWD: Boolean option to enable SVE for the Secure world. SVE is an optional architectural feature for AArch64. Note that this option requires ENABLE\_SVE\_FOR\_NS to be enabled. The default is 0 and it is automatically disabled when the target architecture is AArch32.

- ENABLE\_STACK\_PROTECTOR: String option to enable the stack protection checks in GCC. Allowed values are "all", "strong", "default" and "none". The default value is set to "none". "strong" is the recommended stack protection level if this feature is desired. "none" disables the stack protection. For all values other than "none", the plat\_get\_stack\_protector\_canary() platform hook needs to be implemented. The value is passed as the last component of the option -fstack-protector-\$ENABLE\_STACK\_PROTECTOR.

- ENCRYPT\_BL31: Binary flag to enable encryption of BL31 firmware. This flag depends on DECRYPTION\_SUPPORT build flag.

- ENCRYPT\_BL32: Binary flag to enable encryption of Secure BL32 payload. This flag depends on DECRYPTION\_SUPPORT build flag.

- ENC\_KEY: A 32-byte (256-bit) symmetric key in hex string format. It could either be SSK or BSSK depending on FW\_ENC\_STATUS flag. This value depends on DECRYPTION\_SUPPORT build flag.

- ENC\_NONCE: A 12-byte (96-bit) encryption nonce or Initialization Vector (IV) in hex string format. This value depends on DECRYPTION\_SUPPORT build flag.

- ERROR\_DEPRECATED: This option decides whether to treat the usage of deprecated platform APIs, helper functions or drivers within Trusted Firmware as error. It can take the value 1 (flag the use of deprecated APIs as error) or 0. The default is 0.

- EL3\_EXCEPTION\_HANDLING: When set to 1, enable handling of exceptions targeted at EL3. When set 0 (default), no exceptions are expected or handled at EL3, and a panic will result. This is supported only for AArch64 builds.

- EVENT\_LOG\_LEVEL: Chooses the log level to use for Measured Boot when MEASURED\_BOOT is enabled. For a list of valid values, see LOG\_LEVEL. Default value is 40 (LOG\_LEVEL\_INFO).

- FAULT\_INJECTION\_SUPPORT: ARMv8.4 extensions introduced support for fault injection from lower ELs, and this build option enables lower ELs to use Error Records accessed via System Registers to inject faults. This is applicable only to AArch64 builds.

This feature is intended for testing purposes only, and is advisable to keep disabled for production images.

- FIP\_NAME: This is an optional build option which specifies the FIP filename for the fip target. Default is fip. bin

- FWU\_FIP\_NAME: This is an optional build option which specifies the FWU FIP filename for the fwu\_fip target. Default is fwu\_fip.bin.

- FW\_ENC\_STATUS: Top level firmware's encryption numeric flag, values:

- 0: Encryption is done with Secret Symmetric Key (SSK) which is common for a class of devices.

- 1: Encryption is done with Binding Secret Symmetric Key (BSSK) which is unique per device.

2.5. Build Options 39

This flag depends on DECRYPTION\_SUPPORT build flag.

• GENERATE\_COT: Boolean flag used to build and execute the cert\_create tool to create certificates as per the Chain of Trust described in *Trusted Board Boot*. The build system then calls fiptool to include the certificates in the FIP and FWU\_FIP. Default value is '0'.

Specify both TRUSTED\_BOARD\_BOOT=1 and GENERATE\_COT=1 to include support for the Trusted Board Boot feature in the BL1 and BL2 images, to generate the corresponding certificates, and to include those certificates in the FIP and FWU FIP.

Note that if TRUSTED\_BOARD\_BOOT=0 and GENERATE\_COT=1, the BL1 and BL2 images will not include support for Trusted Board Boot. The FIP will still include the corresponding certificates. This FIP can be used to verify the Chain of Trust on the host machine through other mechanisms.

Note that if TRUSTED\_BOARD\_BOOT=1 and GENERATE\_COT=0, the BL1 and BL2 images will include support for Trusted Board Boot, but the FIP and FWU\_FIP will not include the corresponding certificates, causing a boot failure.

- GICV2\_G0\_FOR\_EL3: Unlike GICv3, the GICv2 architecture doesn't have inherent support for specific EL3 type interrupts. Setting this build option to 1 assumes GICv2 *Group 0* interrupts are expected to target EL3, both by *platform abstraction layer* and *Interrupt Management Framework*. This allows GICv2 platforms to enable features requiring EL3 interrupt type. This also means that all GICv2 Group 0 interrupts are delivered to EL3, and the Secure Payload interrupts needs to be synchronously handed over to Secure EL1 for handling. The default value of this option is 0, which means the Group 0 interrupts are assumed to be handled by Secure EL1.

- HANDLE\_EA\_EL3\_FIRST: When set to 1, External Aborts and SError Interrupts will be always trapped in EL3 i.e. in BL31 at runtime. When set to 0 (default), these exceptions will be trapped in the current exception level (or in EL1 if the current exception level is EL0).

- HW\_ASSISTED\_COHERENCY: On most Arm systems to-date, platform-specific software operations are required for CPUs to enter and exit coherency. However, newer systems exist where CPUs' entry to and exit from coherency is managed in hardware. Such systems require software to only initiate these operations, and the rest is managed in hardware, minimizing active software management. In such systems, this boolean option enables TF-A to carry out build and run-time optimizations during boot and power management operations. This option defaults to 0 and if it is enabled, then it implies WARMBOOT\_ENABLE\_DCACHE\_EARLY is also enabled.

If this flag is disabled while the platform which TF-A is compiled for includes cores that manage coherency in hardware, then a compilation error is generated. This is based on the fact that a system cannot have, at the same time, cores that manage coherency in hardware and cores that don't. In other words, a platform cannot have, at the same time, cores that require HW\_ASSISTED\_COHERENCY=1 and cores that require HW\_ASSISTED\_COHERENCY=0.

Note that, when HW\_ASSISTED\_COHERENCY is enabled, version 2 of translation library (xlat tables v2) must be used; version 1 of translation library is not supported.

- INVERTED\_MEMMAP: memmap tool print by default lower addresses at the bottom, higher addresses at the top. This build flag can be set to '1' to invert this behavior. Lower addresses will be printed at the top and higher addresses at the bottom.

- JUNO\_AARCH32\_EL3\_RUNTIME: This build flag enables you to execute EL3 runtime software in AArch32 mode, which is required to run AArch32 on Juno. By default this flag is set to '0'. Enabling this flag builds BL1 and BL2 in AArch64 and facilitates the loading of SP\_MIN and BL33 as AArch32 executable images.

- KEY\_ALG: This build flag enables the user to select the algorithm to be used for generating the PKCS keys and subsequent signing of the certificate. It accepts 3 values: rsa, rsa\_1\_5 and ecdsa. The option rsa\_1\_5 is the legacy PKCS#1 RSA 1.5 algorithm which is not TBBR compliant and is retained only for compatibility. The default value of this flag is rsa which is the TBBR compliant PKCS#1 RSA 2.1 scheme.

- KEY\_SIZE: This build flag enables the user to select the key size for the algorithm specified by KEY\_ALG. The valid values for KEY\_SIZE depend on the chosen algorithm and the cryptographic module.

| KEY_ALG | Possible key sizes                |  |

|---------|-----------------------------------|--|

| rsa     | 1024, 2048 (default), 3072, 4096* |  |

| ecdsa   | unavailable                       |  |

- Only 2048 bits size is available with CryptoCell 712 SBROM release 1. Only 3072 bits size is available with CryptoCell 712 SBROM release 2.

- HASH\_ALG: This build flag enables the user to select the secure hash algorithm. It accepts 3 values: sha256, sha384 and sha512. The default value of this flag is sha256.

- · LDFLAGS: Extra user options appended to the linkers' command line in addition to the one set by the build system.

- LOG\_LEVEL: Chooses the log level, which controls the amount of console log output compiled into the build. This should be one of the following:

```

0 (LOG_LEVEL_NONE)

10 (LOG_LEVEL_ERROR)

20 (LOG_LEVEL_NOTICE)

30 (LOG_LEVEL_WARNING)

40 (LOG_LEVEL_INFO)

50 (LOG_LEVEL_VERBOSE)

```

All log output up to and including the selected log level is compiled into the build. The default value is 40 in debug builds and 20 in release builds.

• MEASURED\_BOOT: Boolean flag to include support for the Measured Boot feature. If this flag is enabled TRUSTED\_BOARD\_BOOT must be set as well in order to provide trust that the code taking the measurements and recording them has not been tampered with.

This option defaults to 0.

- NON\_TRUSTED\_WORLD\_KEY: This option is used when GENERATE\_COT=1. It specifies the file that contains the Non-Trusted World private key in PEM format. If SAVE\_KEYS=1, this file name will be used to save the key.

- NS\_BL2U: Path to NS\_BL2U image in the host file system. This image is optional. It is only needed if the platform makefile specifies that it is required in order to build the fwu\_fip target.

- NS\_TIMER\_SWITCH: Enable save and restore for non-secure timer register contents upon world switch. It can take either 0 (don't save and restore) or 1 (do save and restore). 0 is the default. An SPD may set this to 1 if it wants the timer registers to be saved and restored.

- OVERRIDE\_LIBC: This option allows platforms to override the default libc for the BL image. It can be either 0 (include) or 1 (remove). The default value is 0.

- PL011\_GENERIC\_UART: Boolean option to indicate the PL011 driver that the underlying hardware is not a full PL011 UART but a minimally compliant generic UART, which is a subset of the PL011. The driver will not access any register that is not part of the SBSA generic UART specification. Default value is 0 (a full PL011 compliant UART is present).

- PLAT: Choose a platform to build TF-A for. The chosen platform name must be subdirectory of any depth under plat/, and must contain a platform makefile named platform.mk. For example, to build TF-A for the Arm Juno board, select PLAT=juno.

- PRELOADED\_BL33\_BASE: This option enables booting a preloaded BL33 image instead of the normal boot flow. When defined, it must specify the entry point address for the preloaded BL33 image. This option is incompatible with EL3\_PAYLOAD\_BASE. If both are defined, EL3\_PAYLOAD\_BASE has priority over PRELOADED\_BL33\_BASE.

- PROGRAMMABLE\_RESET\_ADDRESS: This option indicates whether the reset vector address can be programmed or is fixed on the platform. It can take either 0 (fixed) or 1 (programmable). Default is 0. If the platform has a programmable reset address, it is expected that a CPU will start executing code directly at the right address, both

2.5. Build Options 41

on a cold and warm reset. In this case, there is no need to identify the entrypoint on boot and the boot path can be optimised. The plat\_get\_my\_entrypoint() platform porting interface does not need to be implemented in this case.

- PSCI\_EXTENDED\_STATE\_ID: As per PSCI1.0 Specification, there are 2 formats possible for the PSCI power-state parameter: original and extended State-ID formats. This flag if set to 1, configures the generic PSCI layer to use the extended format. The default value of this flag is 0, which means by default the original power-state format is used by the PSCI implementation. This flag should be specified by the platform makefile and it governs the return value of PSCI\_FEATURES API for CPU\_SUSPEND smc function id. When this option is enabled on Arm platforms, the option ARM\_RECOM\_STATE\_ID\_ENC needs to be set to 1 as well.

- RAS\_EXTENSION: When set to 1, enable Armv8.2 RAS features. RAS features are an optional extension for pre-Armv8.2 CPUs, but are mandatory for Armv8.2 or later CPUs.

When RAS\_EXTENSION is set to 1, HANDLE\_EA\_EL3\_FIRST must also be set to 1.

This option is disabled by default.

- RESET\_TO\_BL31: Enable BL31 entrypoint as the CPU reset vector instead of the BL1 entrypoint. It can take the value 0 (CPU reset to BL1 entrypoint) or 1 (CPU reset to BL31 entrypoint). The default value is 0.

- RESET\_TO\_SP\_MIN: SP\_MIN is the minimal AArch32 Secure Payload provided in TF-A. This flag configures SP\_MIN entrypoint as the CPU reset vector instead of the BL1 entrypoint. It can take the value 0 (CPU reset to BL1 entrypoint) or 1 (CPU reset to SP\_MIN entrypoint). The default value is 0.

- ROT\_KEY: This option is used when GENERATE\_COT=1. It specifies the file that contains the ROT private key in PEM format and enforces public key hash generation. If SAVE\_KEYS=1, this file name will be used to save the key.

- SAVE\_KEYS: This option is used when GENERATE\_COT=1. It tells the certificate generation tool to save the keys used to establish the Chain of Trust. Allowed options are '0' or '1'. Default is '0' (do not save).

- SCP\_BL2: Path to SCP\_BL2 image in the host file system. This image is optional. If a SCP\_BL2 image is present then this option must be passed for the fip target.